1.3.2.1 Configuring Dual Core Demo Main Application

Dual Core Demo Main Application Configurations

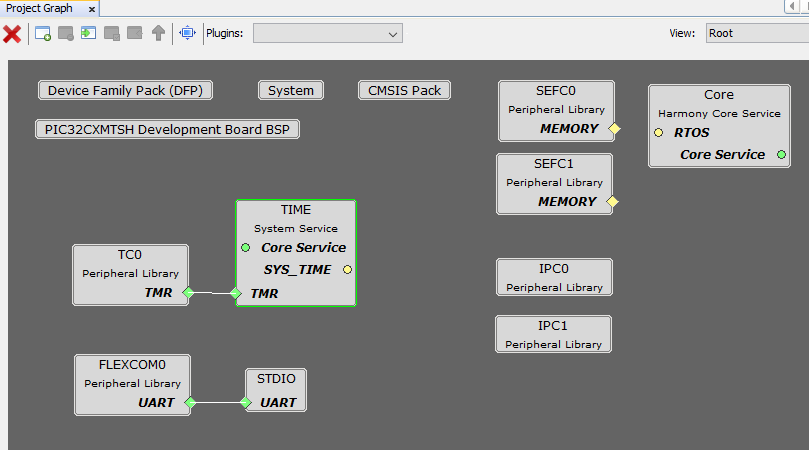

Dual Core Demo Main Application should be configured via MCC. Below is the Snapshot of the MCC configuration window for Dual Core Demo Main Application and some important description.

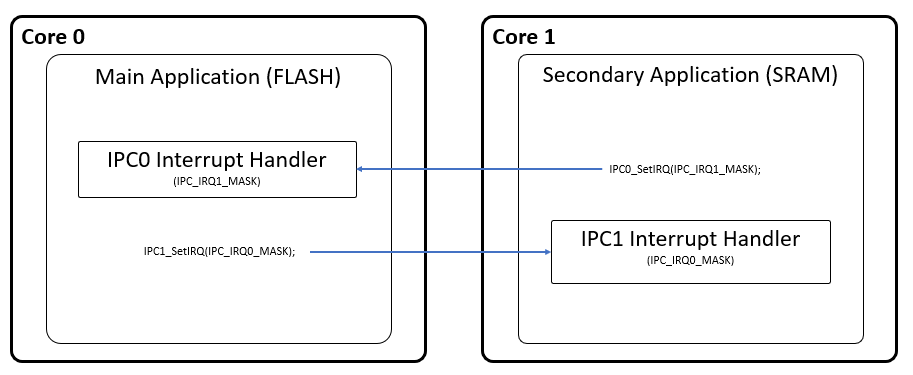

IPC peripheral (IPC0, IPC1) handles the inter-processor communication via interrupt sources. Interrupt sources can be individually generated by writing the Interrupt Set Command (IPC_ISCR) and Interrupt Clear Command (IPC_ICCR) registers. Each interrupt source (IRQ0 to IRQ31) can be enabled or disabled by using the command registers Interrupt Enable Command (IPC_IECR) and Interrupt Disable Command (IPC_IDCR). This set of registers conducts enabling or disabling of an instruction.

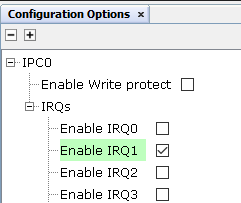

IPC0:

IPC0 Interrupt Handler is responsible for capturing the interrupt signal (IPC_IRQ1_MASK) triggered by the Secondary Application. Therefore IRQ1 must be enabled.

IPC0 initialization is required.

IPC_IRQ1_MASK signal is used to send command from the Secondary core to the Main core.

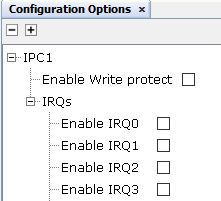

Figure . Dual Core Demo IPC0 configuration

IPC1:

IPC1 is only used to send commands from Main core to the Secondary core, no interrupt handler is required. Therefore IRQs must be disabled.

IPC_IRQ0_MASK signal is used to send command from the Main core to the Secondary core.

Figure . Dual Core Demo IPC1 configuration

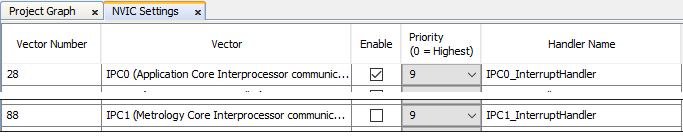

NVIC Settings:

Since only IPC0 interrupt is required, only the IPC0_InterruptHandler must be enabled.

Figure . Dual Core Demo IPC NVIC Settings

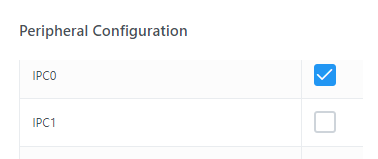

Peripheral Clock:

The Main core enables the IPC0 peripheral clock but not IPC1 peripheral clock, which is enabled by the Secondary core.

Figure . Dual Core Demo IPC Peripheral Clocks

Initialization Routine:

Peripherals used by the Main and Secondary application simultaneously must been only initialized and configured by the Main application.

Peripherals used only by the Secondary application must be configured by the Secondary application.

Peripherals included in the subsystem 1 (secondary) must be initialized by the Secondary application due to the recommended programming sequence for powering up the Secondary core.

NVIC Interrupt vector must be configured independently in each application.

void SYS_Initialize ( void* data )

{

/* MISRAC 2012 deviation block start */

/* MISRA C-2012 Rule 2.2 deviated in this file. Deviation record ID - H3_MISRAC_2012_R_2_2_DR_1 */

SEFC0_Initialize();

SEFC1_Initialize();

DWDT_Initialize();

CLK_Initialize();

PIO_Initialize();

SUPC_Initialize();

RSTC_Initialize();

TC0_CH0_TimerInitialize();

IPC0_Initialize();

FLEXCOM0_USART_Initialize();

BSP_Initialize();

sysObj.sysTime = SYS_TIME_Initialize(SYS_TIME_INDEX_0, (SYS_MODULE_INIT *)&sysTimeInitData);

APPCORE0_Initialize();

NVIC_Initialize();

/* MISRAC 2012 deviation block end */

}Recommended Programming Sequence for Secondary core:

This programming sequence must be performed at some point of the Main application.

The following steps should be performed to ensure an optimum Secondary core start-up procedure:

Assert reset of the coprocessor and its peripherals

Disable coprocessor Clocks

Disable coprocessor peripheral clocks

De-assert reset of the coprocessor peripherals

Enable coprocessor peripheral clocks

Load all secondary sections.

De-assert the reset of the coprocessor (Core 1)

Enable the coprocessor clock (Core 1)

static void _APPCORE0_CoprocessorInitialize(void)

{

uint32_t tmp;

/* Assert reset of the coprocessor and its peripherals */

tmp = RSTC_REGS->RSTC_MR;

tmp &= ~(RSTC_MR_CPROCEN_Msk | RSTC_MR_CPEREN_Msk);

RSTC_REGS->RSTC_MR = RSTC_MR_KEY_PASSWD | tmp;

/* Disable coprocessor Clocks */

PMC_REGS->PMC_SCDR = PMC_SCDR_CPKEY_PASSWD | PMC_SCDR_CPCK_Msk;

/* Disable coprocessor peripheral clocks */

PMC_REGS->PMC_SCDR = PMC_SCDR_CPKEY_PASSWD | PMC_SCDR_CPBMCK_Msk;

/* De-assert reset of the coprocessor peripherals */

RSTC_REGS->RSTC_MR |= RSTC_MR_KEY_PASSWD | RSTC_MR_CPEREN_Msk;

/* Enable coprocessor peripheral clocks */

PMC_REGS->PMC_SCER = PMC_SCER_CPKEY_PASSWD | PMC_SCER_CPBMCK_Msk;

__xc32_LoadAllSecondarySections();

/* De-assert the reset of the coprocessor (Core 1) */

RSTC_REGS->RSTC_MR |= (RSTC_MR_KEY_PASSWD | RSTC_MR_CPROCEN_Msk);

/* Enable the coprocessor clock (Core 1) */

PMC_REGS->PMC_SCER = (PMC_SCER_CPKEY_PASSWD | PMC_SCER_CPCK_Msk);

}