1.2.5.4 Ethernet GMAC Driver Library

The Ethernet Media Access Controller (GMAC) module implements a 10/100 Mbps Ethernet MAC, compatible with the IEEE 802.3 standard. The GMAC can operate in either half or full duplex mode at all supported speeds.

Embedded Characteristics

Compatible with IEEE Standard 802.3

10, 100 Mbps operation

Full and half duplex operation at all supported speeds of operation

Statistics Counter Registers for RMON/MIB

MII interface to the physical layer

Integrated physical coding

Direct memory access (DMA) interface to external memory

Support for 6 priority queues in DMA

8 KB transmit RAM and 4 KB receive RAM

Programmable burst length and endianism for DMA

Interrupt generation to signal receive and transmit completion, errors or other events

Automatic pad and cyclic redundancy check (CRC) generation on transmitted frames

Automatic discard of frames received with errors

Receive and transmit IP, TCP and UDP checksum offload. Both IPv4 and IPv6 packet types supported

Address checking logic for four specific 48-bit addresses, four type IDs, promiscuous mode, hash matching of unicast and multicast destination addresses and Wake-on-LAN

Management Data Input/Output (MDIO) interface for physical layer management

Support for jumbo frames up to 10240 Bytes

Full duplex flow control with recognition of incoming pause frames and hardware generation of transmitted pause frames

Half duplex flow control by forcing collisions on incoming frames

Support for 802.1Q VLAN tagging with recognition of incoming VLAN and priority tagged frames

Support for 802.1Qbb priority-based flow control

Programmable Inter Packet Gap (IPG) Stretch

Recognition of IEEE 1588 PTP frames

IEEE 1588 time stamp unit (TSU)

Support for 802.1AS timing and synchronization

Supports 802.1Qav traffic shaping on two highest priority queues

Abstraction Model

The Ethernet Controller provides the modules needed to implement a 10/100 Mbps Ethernet node using an external Ethernet PHY chip. The PHY chip provides a digital-analog interface as part of the Physical Layer and the controller provides the Media Access Controller (MAC)_layer above the PHY.

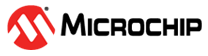

As shown in figure below, the Ethernet Controller consists of the following modules:

Media Access Control (MAC) block: Responsible for implementing the MAC functions of the Ethernet IEEE 802.3 Specification

Flow Control (FC) block: Responsible for control of the transmission of PAUSE frames. (Reception of PAUSE frames is handled within the MAC.)

RX Filter (RXF) block: This module performs filtering on every receive packet to determine whether each packet should be accepted or rejected

TX DMA/TX Buffer Management Engine: The TX DMA and TX Buffer Management engines perform data transfers from the memory (using descriptor tables) to the MAC Transmit Interface

RX DMA/RX Buffer Management Engine: The RX DMA and RX Buffer Management engines transfer receive packets from the MAC to the memory (using descriptor tables)

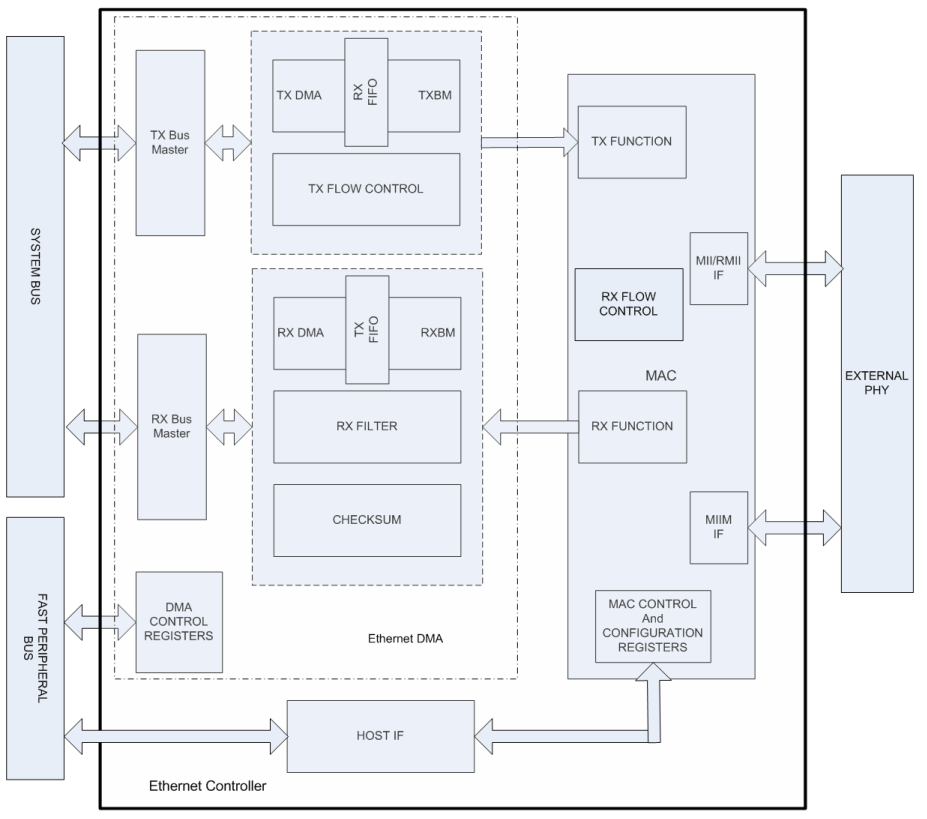

For completeness, we also need to look at the interface diagram of a representative Ethernet PHY. As shown in Figure 2, the PHY has two interfaces, one for configuring and managing the PHY (SMI/MIIM) and another for transmit and receive data (RMII or MII). The SMI/MIIM interface is the responsibility of the Ethernet PHY Driver Library. When setting up the Ethernet PHY, this Ethernet driver calls primitives from the Ethernet PHY Driver library. The RMII/MII data interface is the responsibility of the Ethernet MAC Driver Library (this library).

Library Interface

| Name | Description |

|---|---|

| Client Level Functions | |

| DRV_GMAC_Close | Closes a client instance of the PIC32 MAC Driver. |

| DRV_GMAC_Open | Opens a client instance of the PIC32 MAC Driver. |

| DRV_GMAC_Deinitialize | Deinitializes the PIC32 Ethernet MAC. |

| DRV_GMAC_Initialize | Initializes the PIC32 Ethernet MAC. |

| DRV_GMAC_Reinitialize | Reinitializes the PIC32 Ethernet MAC. |

| Receive Functions | |

| DRV_GMAC_PacketRx | This is the MAC receive function. |

| DRV_GMAC_RxFilterHashTableEntrySet | Sets the current MAC hash table receive filter. |

| Transmit Functions | |

| DRV_GMAC_PacketTx | MAC driver transmit function. |

| Event Functions | |

| DRV_GMAC_EventAcknowledge | Acknowledges and re-enables processed events. |

| DRV_GMAC_EventMaskSet | Enables/disables the MAC events. |

| DRV_GMAC_EventPendingGet | Returns the currently pending events. |

| Other Functions | |

| DRV_GMAC_ConfigGet | Gets the current MAC driver configuration. |

| DRV_GMAC_LinkCheck | Checks current link status. |

| DRV_GMAC_ParametersGet | MAC parameter get function. |

| DRV_GMAC_PowerMode | Selects the current power mode for the Ethernet MAC. |

| DRV_GMAC_Process | MAC periodic processing function. |

| DRV_GMAC_RegisterStatisticsGet | Gets the current MAC hardware statistics registers. |

| DRV_GMAC_Status | Provides the current status of the MAC driver module. |

| DRV_GMAC_StatisticsGet | Gets the current MAC statistics. |

| DRV_GMAC_Tasks | Maintains the EThernet MAC driver's state machine. |

| Data Types and Constants | |

| DRV_GMAC_INDEX_COUNT | Number of valid Ethernet driver indices. |

| _DRV_GMAC_H | This is macro _DRV_GMAC_H. |