1.1 UART Bootloader

The UART bootloader Library can be used to upgrade firmware on a target device without the need for an external programmer or debugger.

Features

Supported on CORTEX-M and MIPS based MCUs, and MPUs

Uses Harmony 3 UART PLIB to communicate resulting in smaller bootloader size

Supports Fail Safe update for the devices which have a Dual Bank flash memory

Takes Binary File as input

Uses command line host script to receive binary from Host PC

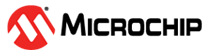

Running From SRAM (For CORTEX-M Devices)

Supports simultaneous Flash memory write and reception of the next block of data, Achieved by loading bootloader into flash and running from SRAM

Has capability to self update as it is running from SRAM

At reset the bootloader Reset handler copies the entire bootloader firmware into SRAM from Start location and start executing from SRAM

Once the application is called from bootloader, applications startup code takes control over SRAM and starts executing

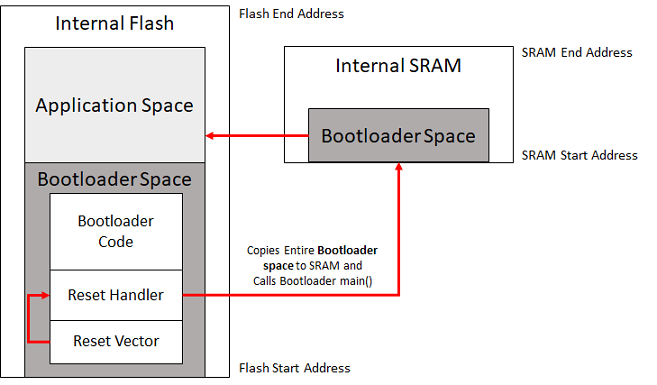

UART Bootloader Block Diagram

Input Task:

This task is responsible for receiving data from Host-PC through the UART communication interface

The task keeps polling for data to be received when bootloader is in idle mode

The task also validates the incoming packet from host with expected header information

Once the packet reception is completed it gives control to Command Task

Command Task:

This task processes the commands received from Input Task and provides response back to host accordingly

If the command received is a Data command it gives control to the Flash Task

Flash Task:

This task is responsible to program the internal flash memory with data packet received

The task uses the NVM peripheral library to perform the Unlock/Erase/Write Operations

The task also invokes Input Task in parallel to receive next packet while waiting for the flash operation to complete for CORTEX-M based MCUs

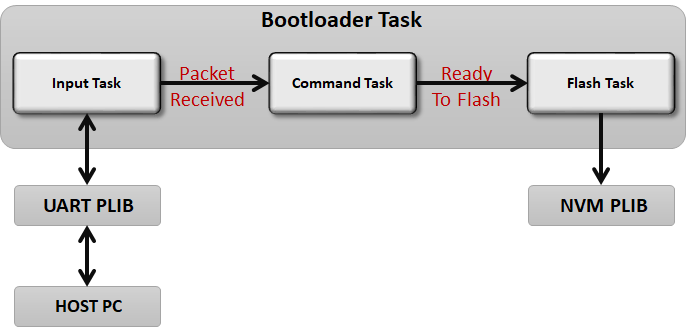

MPU UART Bootloader

MPU UART bootloader performs the following functions:

It loads the harmony application from SD/eMMC/NAND/Serial Flash memory to the DDR memory and executes it

It receives new harmony application image and writes it to SD/eMMC/NAND/Serial Flash memory

Input Task:

This task is responsible for receiving data from Host-PC through the UART communication interface

The task keeps polling for data to be received when bootloader is in idle mode

The task also validates the incoming packet from host with expected header information

Once the packet reception is completed it gives control to Command Task

Command Task:

This task processes the commands received from Input Task and provides response back to host accordingly

If the command received is a Data command it gives control to the Programming Task

Programming Task:

This task is responsible to program the SD/eMMC/NAND/Serial Flash memory with data packet received

The task uses the following System service or Driver to perform the Unlock/Erase/Write/Read Operations

MPU UART bootloader with SD/eMMC media uses SYS_FS (FAT-FS) API to perform the Write/Read Operations

MPU UART bootloader with NAND Flash media uses NAND Flash Driver API to perform the Unlock/Erase/Write/Read Operations

MPU UART bootloader with Serial Flash media uses FLASH Driver (e.g. SST26 Driver) API to perform the Unlock/Erase/Write/Read Operations